Sequential Logic

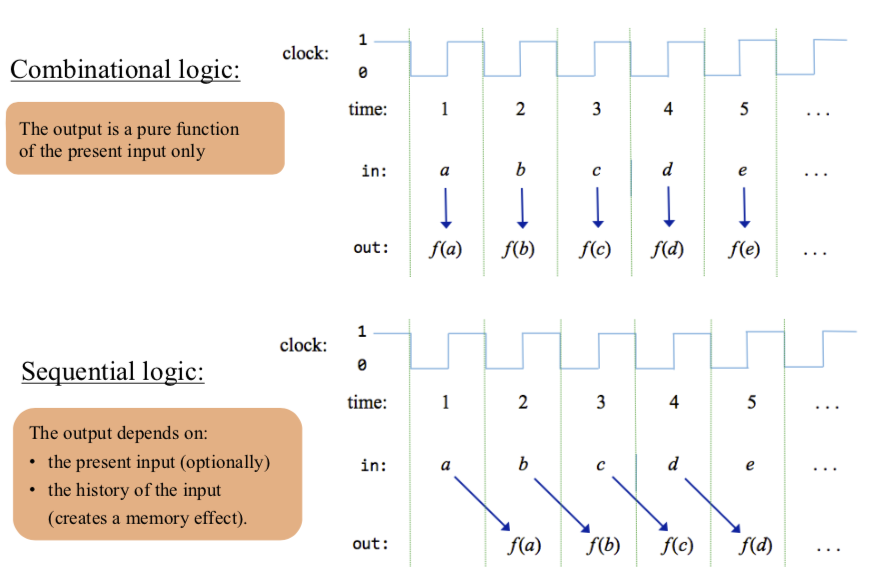

Combinational chips compute functions that depend solely on combinations of their input values. These relatively simple chips provide many important processing functions (like the ALU), but they cannot maintain state. Since computers must be able to not only compute values but also store and recall values, they must be equipped with memory elements that can preserve data over time. These memory elements are built from sequential chips.

Flip-Flop

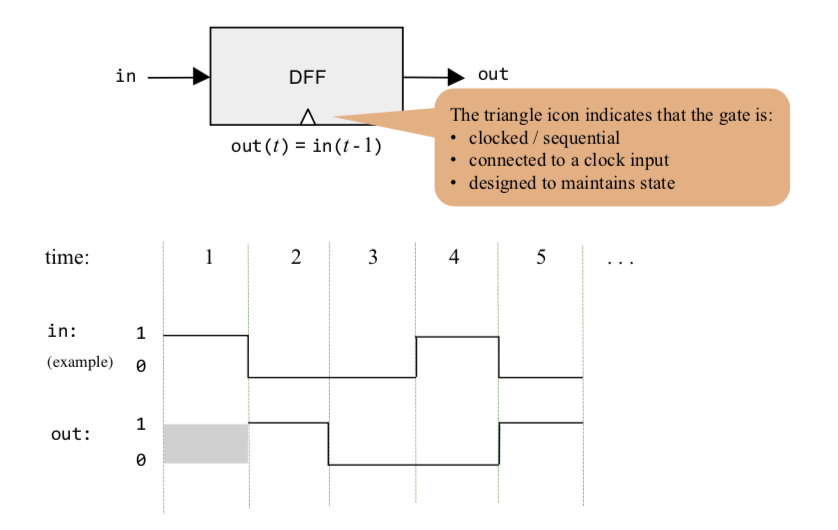

- the DFF has a clock input that continuously changes according to the master clock’s signal.

- 1-bit input, 1-bit output

- The gate outputs its previous input:

\[out(t)=in(t-1)\]

- Implementation: a gate that can flip between two stable states: remembering 0, or remembering 1

- Gates that feature this behavior are called data flip-flops.

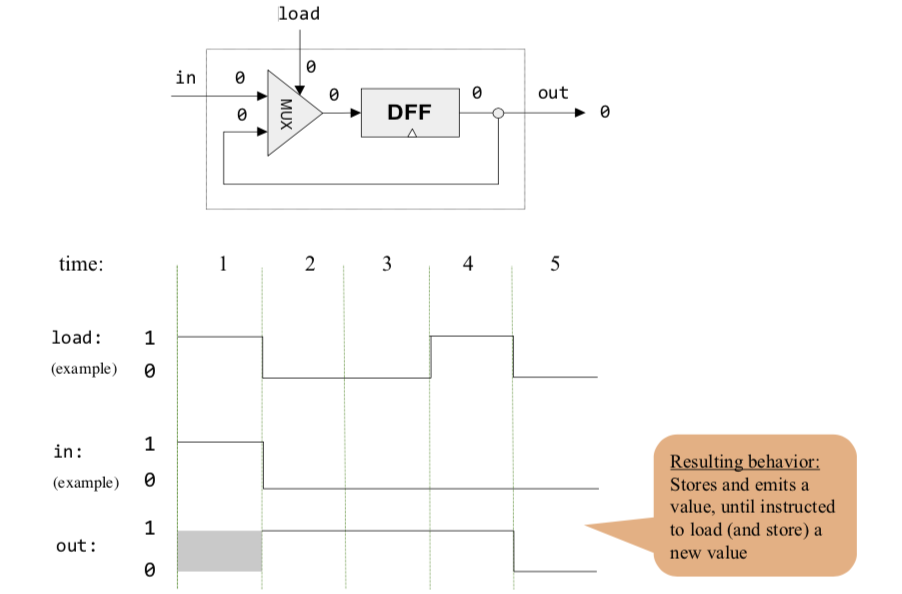

1-bit register

A single-bit register, which we call Bit, or binary cell, is designed to store a single bit of information (0 or 1). The chip interface consists of

- an input pin that carries a data bit;

- a load pin that enables the cell for writes;

- an output pin that emits the current state of the cell

read/write behavior

- Read: To read the contents of a register, we simply probe its output.

- Write: To write a new data value d into a register, we put d in the in input and assert (set to 1) the load input. In the next clock cycle, the register commits to the new data value, and its output starts emitting d.

1 | /** |

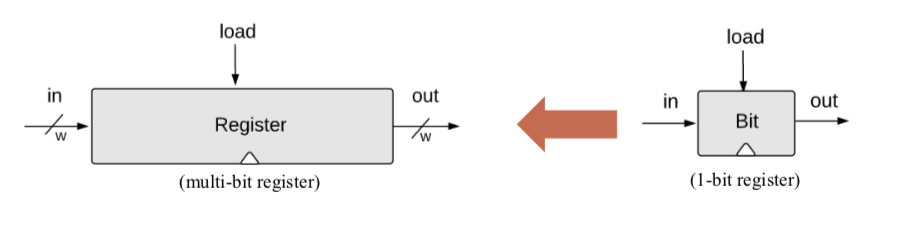

Multi-bit register (also known as “register”)

A w-bit register can be created from an array of w 1-bit registers.

1 | /** |

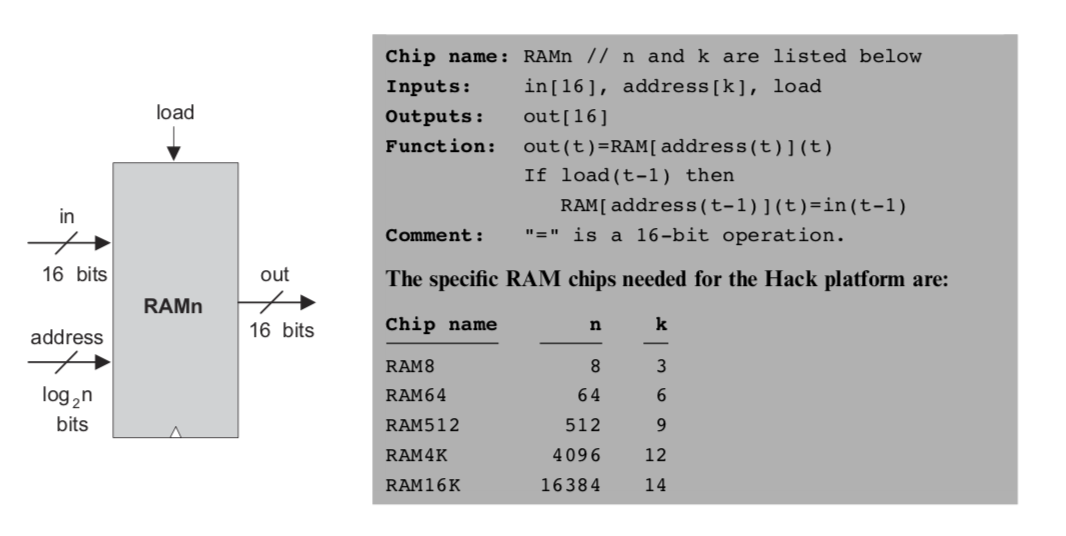

Random Access Memory (RAM)

Architecture A sequence of n addressable registers, with addresses 0 to n-1

The number of registers (n) and the width of each register (w) are called the memory’s size and width

Address width \[k = log_2 n\]

To read Register i:

- set address = i

- probe out

To set Register i to v:

- set address = i

- set in = v

- set load = 1

1 | /** |

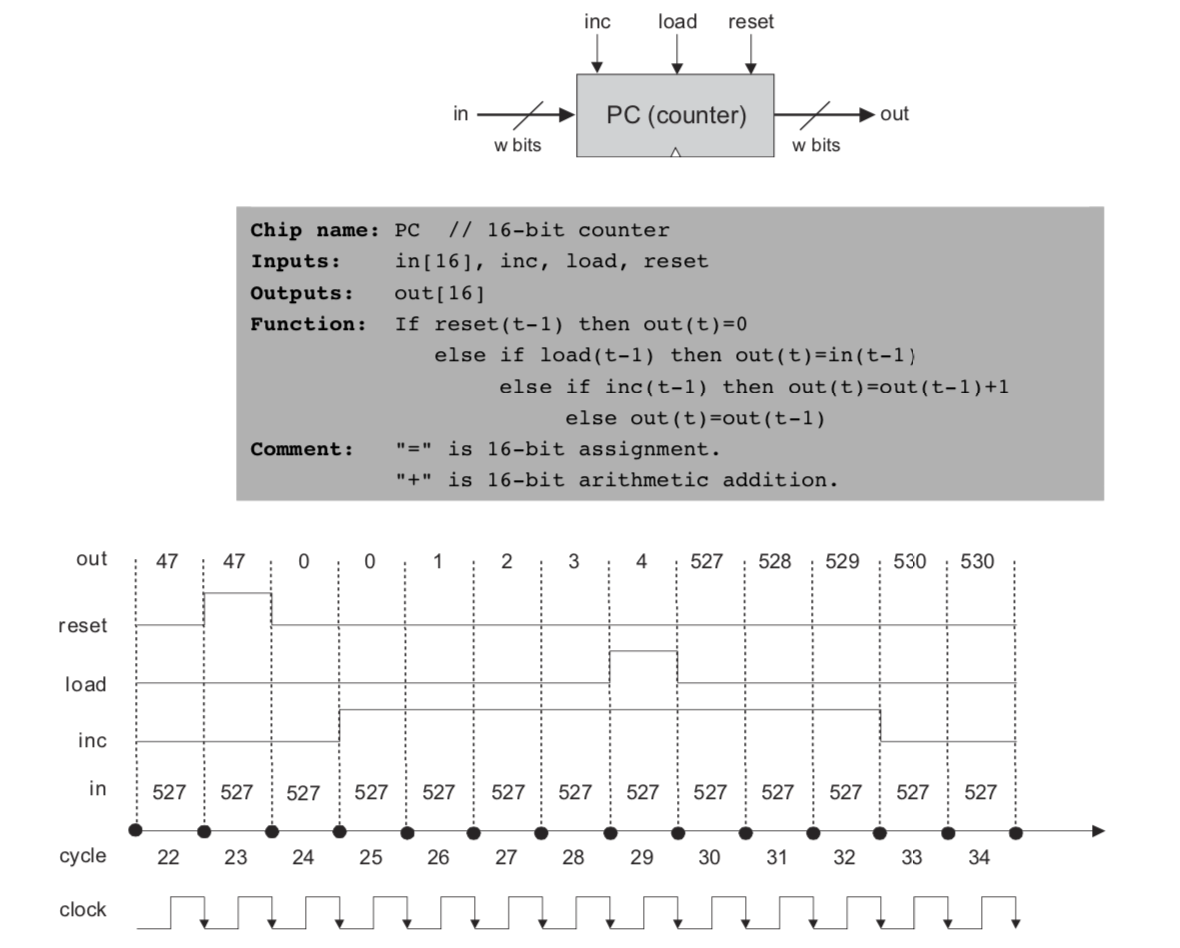

Program Counter

- The computer must keep track of which instruction should be fetched and executed next

- This control mechanism can be realized by a register called Program Counter

- The PC contains the address of the instruction that will be fetched and executed next

- The PC is designed to support three possible control operations:

- Reset: fetch the first instruction (PC = 0)

- Next: fetch the next instruction (PC++)

- Goto: fetch instruction n(PC = n)

1 | /** |